# QONO

# **Understanding Thermal Analysis of RF Devices**

**Thermal Design from an Application Perspective**

### Introduction

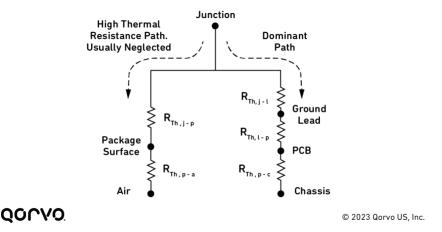

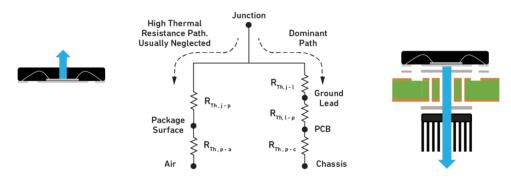

Thermal design and analysis are critical to improving component reliability. This document provides information related to thermal analysis and functionality for Qorvo<sup>®</sup> products and their applications. It outlines the basics of thermal design, such as resistive analysis shown in **Figure 1**, for Qorvo components in customer applications and describes details to assist engineers with their system-level design.

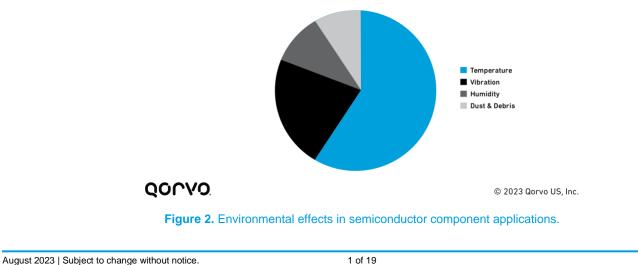

From an environmental perspective, temperature is the biggest reason most semiconductors fail in their field application, as shown in **Figure 2**. This can be due to a harsh operating environment without adequate protections built in at the system level, which in turn can result from an incomplete understanding of the thermal aspects of semiconductor devices, packaging, layout and heat sinking. In addition, thermal measurements on RF devices at design verification can be a bit tricky.

In this document we will break down the many aspects of temperature and design for RF semiconductor product applications. The goal is to help you design easier, faster and more reliably, so your systems do not break down due to thermal issues.

Richardson

**Electronics**

R & MICRO

**Technology**

Partner

www.qorvo.com

800.348.5580

630.208.2200

### **Table of Contents**

- 1. Introduction

- 2. Table of Contents

- 3. Reference Documents

- 4. The Basics of Semiconductor Thermal Measurement

- 5. Thermal Resistance

- 6. Determining Junction or Channel Temperature

- 7. A Review of Application Material Properties

- 8. Thermal Vias in an Application

- 9. Thermal Interfaces

- 10. Thermal Measurement Methods for an Application

- 11. High-Power GaN Application Considerations

- a. Thermal Measurement

- b. Improving Thermal Conductivity in Applications

- i. Die Only Applications

- ii. QFN and Surface Mount Packaged Applications

- iii. Copper Plated (CP) and Flange Packaged Applications

- 12. System Level Thermal Analysis

- 13. In-Closing

- 14. Definitions

- 15. Additional Information

- 16. Contact Information

August 2023 | Subject to change without notice.

### **Referenced Documents**

The reference documents below take precedence over the contents of this application note and should always be consulted for the latest information.

### Application Note: GaN Device Channel Temperature, Thermal Resistance and Reliability Estimates:

https://www.gorvo.com/products/d/da006480

#### Video: Understanding GaN Thermal Analysis:

https://www.qorvo.com/design-hub/videos/understanding-gan-thermal-analysis

Application Note: GaN Thermal Analysis for High-Performance Systems: https://www.qorvo.com/resources/d/qorvo-gan-thermal-analysis-for-high-performance-systems-white-paper

Application Note: High-Performance GaN Thermal Evaluation – Limitations of Infrared Microscopy: https://www.qorvo.com/resources/d/qorvo-high-performance-gan-thermal-evaluation-infrared-microscopy-limitations

# Application Note: Application of Arctic Silver 5 Thermal Compound and Indium Shims for Qorvo CP-style Packaged Components: https://www.qorvo.com/products/d/da006842

White Paper: GaAs and GaN Die Assembly and Handling Procedure: https://www.qorvo.com/resources/d/qorvo-gaas-gan-die-assembly-handling-procedures-white-paper

### White Paper: CW Operation of QFN-Packaged Pulsed GaN Power Amplifiers: https://www.qorvo.com/resources/d/cw-operation-of-qfn-packaged-pulsed-gan-power-amplifiers-white-paper

#### Application Note: Bulk Thermal Models:

Available upon request from applications engineering.

August 2023 | Subject to change without notice.

### The Basics of Semiconductor Thermals and Measurement

Let's begin with some thermal basics. Temperature is a simple measurement of hot or cold - and heat is simply the energy of the atoms in a solid or fluid. When talking about heat flow - thermal conduction is the transfer of internal energy by microscopic collisions of particles and movement of electrons within a material. In any semiconductor component or system design, we must consider the thermal aspect to ensure our end product is reliable, performs optimally, meets certification criteria and works in all end product environments. To ensure these criteria are met, we need to know the device temperature and how to control it.

Heat will always move from hot to cold or cooler temperatures. Additionally, the amount of heat passing through something like a semiconductor or PC board depends on the thermal conductance of the material and the temperature on either side. The lower the thermal conductance of the material the less heat will pass through for a given temperature drop ( $\Delta T$ ) – which can be detrimental to the semiconductor device. In a semiconductor application we always strive to provide the highest thermal conductance possible for efficient heat removal from the semiconductor or heat source. The reciprocal of thermal conductance is termed thermal resistance, which we wish to minimize.

In electronics, engineers use terms like junction or channel temperature, maximum temperature, heat dissipation and power dissipation, which all can be used to describe heat generation or the impacts thereof. When you review any data sheet you need to understand these terms and how the thermal data lines up with your application.

Generally speaking, in our product designs, we want to control or keep the semiconductor device as close to room temperature (75°F or 25°C) as possible so our semiconductor products meet their optimum electrical performance. But as we know, this is almost never possible without a controlled environment.

The first step in understanding system thermal measurements is looking at the semiconductor itself. The device data sheet will provide valuable device thermal information, which can be used to determine the highest temperature or power dissipation it can handle. The data sheet reference is a good start, but in an application setting, all device interactions must also be considered. On the device data sheet, manufacturers can use several methods of measuring and providing device thermal data.

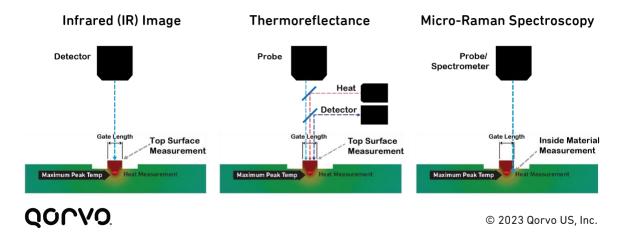

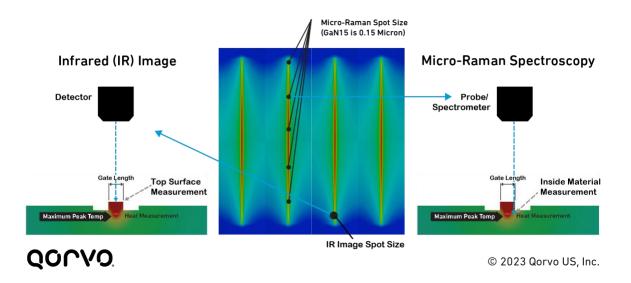

From a semiconductor perspective there are three main ways manufacturers optically measure junction or channel temperature (Tj or Tch) – infrared (IR) image, thermoreflectance, and micro-Raman spectroscopy. Additionally, companies will use computer models to estimate device and system-level temperatures in a given application. Below, Figure 3 shows the way these three methods are applied.

Figure 3. IR imaging, thermoreflectance and micro-Raman thermal measurement.

Note, all three of these above methods in Figure 3 measure temperature without touching the surface of the semiconductor. IR imaging simply measures the thermal radiation coming off the surface of the semiconductor. Thermoreflectance provides its own radiation at the surface and then detects it in addition to the surface's natural radiation (which then gets subtracted out). Micro-Raman is a more expensive and time-consuming measurement technique, but it is the most accurate because it measures the temperature within the epitaxial layer with extreme resolution.

August 2023 | Subject to change without notice.

Richardson **Electronics** VER & MICROWAVE

# QOUNO

### **Thermal Resistance**

Thermal resistance is the measurement of a material's ability to resist heat flow. In general, when talking about semiconductors, we would like our semiconductor material, bonding material, PC board material, etc., to have a very low thermal resistance level, so heat flows freely to the ambient air. So, in semiconductor applications, low thermal resistance (Rth) is our goal. **Figure 4** illustrates some of the formulas associated with heat transfer and thermal measurement.

- Thermal conductivity the ability of a given material to conduct/transfer heat.

- Thermal resistivity the ability of a given material to resist the conduction/transfer of heat.

- Thermal resistance is like resistivity but takes the shape and size of the material into account.

- Thermal impedance is like resistance but does not factor in the footprint size of the material and often includes interfacial resistances to provide an effective value for a layer within a stack.

- Thermal Conductivity = k • Thermal Resistance =  $\frac{l}{(k)(A)}$ • Thermal Resistivity =  $\frac{1}{k}$ • Thermal Impedance =  $\frac{l}{k}$

- *l* = is the material thickness.

- A = is the material cross-sectional area normal to the direction of heat flow.

- *k* = k-value of a material determines how quickly heat can spread through it.

- Temperature Change °C = Rth Junction to Case × Pdiss Watts

- Max. Junction Temperature at Max. Case (Tbase) Temp = Temp Change °C + Max. Case Temp °C

- Tbase = Interface Between Part and PC Board/Heatsink

© 2023 Qorvo US, Inc.

#### Figure 4. Physics of heat conduction - thermal resistance formulas and application calculation.

The analogy of an electrical resistor network in Figure 4 illustrates the thermal resistance of a packaged semiconductor device. This represents the electrical resistor equivalent circuit – starting from the heat source (transistor junction or channel) through the two possible pathways the heat will transfer. In this electrical resistor model, the electrical resistance is defined by the potential difference (voltage) across the resistor divided by the current through that resistor. In thermal resistance, the thermal potential difference (temperature) divided by the thermal current (heat flow) through the thermal resistor defines the thermal resistance Rth.

In the first pathway, heat transfers from the transistor junction or channel through the mold compound by conduction, and then to the air surrounding the device by convection. In the second pathway (dominant path), which is parallel with the first, heat flows from the junction or channel of the device through the lead, through the PC board, into the chassis by conduction and finally to the air surrounding it by convection. The second path is the primary focus of calculating the junction or channel temperature since the majority of the heat generated in the device transports through this pathway. This pathway is also the one we will concentrate on in detail in this application note.

August 2023 | Subject to change without notice.

V A Richardson Electronics

ER & MICRO

www.qorvo.com

800.348.5580

630.208.2200

### **Determining Junction or Channel Temperature**

Let's start with the basics of measuring the thermal properties of semiconductors. The most popular method of determining the junction or channel temperature (Tj or Tch) of a semiconductor device is using IR imagery. IR imagery is common and accessible. It is generally very reliable, easy to operate and provides important thermal data quickly. An IR image measures the topside of the die to determine the temperature and has a maximum resolution measurement of three to five microns. See **Figure 5**.

In some instances, such as measuring Gallium Nitride (GaN) semiconductors, a more precise measurement is required to determine the exact junction or channel temperature. In these cases, more precision equipment is required. This is where a micro-Raman measurement is needed. micro-Raman measures into the epitaxial layer with a spot size of 0.15 microns, which provides a more accurate maximum junction measurement. To learn more about micro-Raman measurements of GaN, please refer to the Qorvo App Note, *GaN Device Channel Temperature, Thermal Resistance and Reliability Estimates*.

#### Figure 5. IR Imaging versus micro-Raman thermal measurement (Note: micro-Raman measures below the material surface).

Note most companies use IR imagery to make this Tj or Tch determination, as it is the easiest to use, cost-effective and most accessible, but it provides a lower measurement value due to averaging across the surface region above the channel.

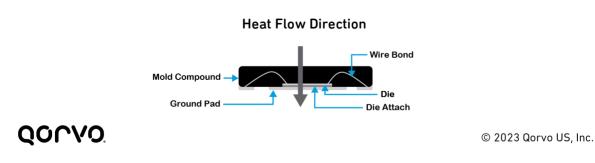

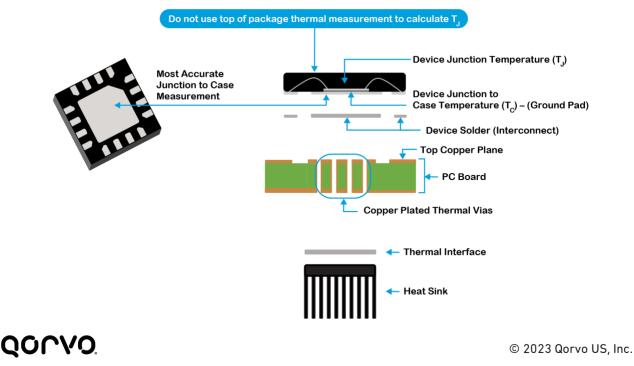

Let's review some basics of measuring an application using a molded semiconductor on a PC board. As shown in **Figure 6**, there are several layers and measurement areas to consider when looking at thermal measurements of your application. The first thing to consider is the heat path. In a package as shown in Figure 6, the heat path for this type of design must go through the bottom of the package through the ground pad. Therefore, the application design should incorporate a PC board that pulls the heat from the bottom of the package through the device ground slug. Note, in this type of package, attempting to draw heat from the top of the package will not work due to the poor thermal conductivity of the mold compound; trying to cool from the top will cause device degradation/failure due to high junction/channel temperature. The primary heat paths in semiconductors require heat to be pulled away from the device through the bottom of the die in the most effective way possible (unless the manufacturer notes otherwise). Therefore, in this scenario, pulling the heat down through the ground pad represents the lowest resistance to heat flow from the device junction or channel to the outside world.

August 2023 | Subject to change without notice.

Figure 6. This overmolded part shows heat flows from the top of the die down through the package ground pad.

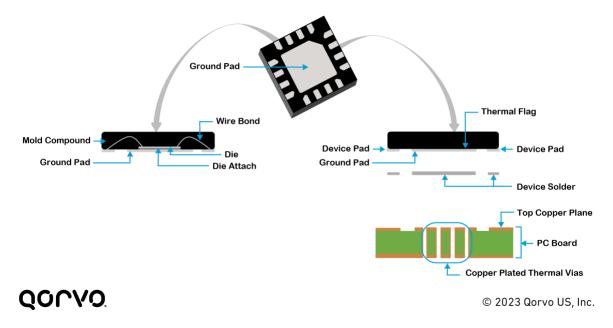

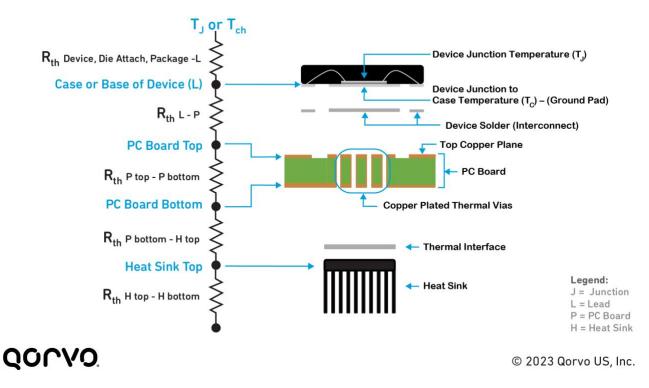

**Figure 7** illustrates the layers of an application using a packaged part. Note, when designing a system or final product, it is important to use as much information and material from the semiconductor vendor as possible, such as S2P parameters, PC board Gerber files, etc., so the proper thermal heat extraction methods are employed. For example, placement of via holes and creation of these vias are very important to extract heat from your device and increase part reliability – these types of instructions and placements of via holes are generally located in the PC board Gerber files offered by the semiconductor vendor.

#### Figure 7. Application cut-away showing layers and component parts.

As you can see in Figures 6 and 7, the semiconductor device is located above the ground pad of the device using a die attach material. Between the ground slug and the PC board will be the solder attach, which should be a high-grade material effective for optimizing thermal dissipation. The via holes' location, size, and style are typically spelled out by the vendor for optimized performance and should be used with vendor direction. The placement, style, and type of via holes are important. We will dig deeper into this later in this application note.

August 2023 | Subject to change without notice.

Technology Partner

# QONOD

**Figure 8** below shows the electrical Rth equivalent circuit for a semiconductor device application shown in Figure 7. As seen in Figure 8, the largest portion of the thermal path goes through the devices, die attach and package ground pad into the PC board vias through solder. It is critical the vias are precisely made to ensure a low resistance pathway for the heat. The amount of variation between PC board materials and design can be significant (see **Table 1**); therefore, airflow, board size, board thickness, via hole location and type can all affect the thermal resistance of the PC board. Moreover, the solder attachment material and methodology are also critical here. When using a heat sink as shown in the image, attaching the heat sink to the lowest impedance path to the IC junction or channel is best.

Figure 8. Thermal resistance layers in typical semiconductor application.

August 2023 | Subject to change without notice.

### **A Review of Application Material Properties**

The most well-known property to consider when reviewing materials for a given device or application is thermal conductivity. This is designated by a lowercase "k". One important thing to note is that metals and ceramics have significantly higher thermal conductivities than polymers and composites which leads to very little heat transfer through these materials.

The k-value of a material determines how fast heat can spread through it. A high k-value means better heat conduction. For metal, the k-value usually increases along with the electrical conductivity. Many dielectric materials have a high k-value, as shown in the tables in **Figure 9**. Moreover, a material's k-value has some dependence on temperature and may be anisotropic or direction dependent.

Good Thermal PropertiesMaterialK (at 25°C)Diamond2000Silver429Copper401Silicon Carbide370

### **Poor Thermal Properties**

| Material               | K (at 25°C)       |

|------------------------|-------------------|

| Glass, Ordinary        | 0.8               |

| Rogers 4003 Dielectric | 0.7 (z-Direction) |

| FR4 Dielectric         | 0.3 (z-Direction) |

| Air                    | 0.026             |

Q0000

© 2023 Qorvo US, Inc.

#### Figure 9. Material property and thermal conductivity (k).

Although copper is a great conductor and a common ingredient in electronics packaging, not all copper is the same. As shown in **Table 1**, sometimes the process used to fabricate the copper will change the k-value. Generally speaking, copper is affected by both the alloy and process techniques. For example, copper lead-frames for over-molded QFNs use an alloy with a k-value 35% lower than pure copper (copper-110), while the plated copper in PC boards will have a k-value that is around 15% lower than a rolled copper foil that starts out on a board.

| Usage                | Alloy/Composition                            | Thermal Conductivity $\left(rac{W}{mK} ight)$ | Process                    |

|----------------------|----------------------------------------------|------------------------------------------------|----------------------------|

| Etched Leadframe     | ASTM B465 (CDA194)<br>(2.4% Fe + Some Zn, P) | 260                                            | Etched/Rolled/Stamped      |

| Intricate Heat Sinks | Various Cu Powder<br>Metallurgies            | 300-380                                        | Sintering (< 100% density) |

| Laminate Via         | Copper with<br>Plating Bath Impurities       | 330-350                                        | Plated (< 100% density)    |

| High-k Leadframe     | ASTM B747 (Cu-151)<br>(0.1% Zn)              | 368                                            | Etched/Rolled/Stamped      |

| -CP Pkg Baseplate    | ASTM B152<br>(Copper 110)                    | 400                                            | Stamped/Forged             |

Table 1. Table detailing types of copper used in PC board manufacture.

Additionally, the PC boards' thermal resistance is proportional to the overall thickness of the board – and thermal vias also play a part in this resistance value. Thus, a very thin PC board like 8-mils is often used for high-power GaN in a QFN package to keep the thermal resistance as low as possible.

August 2023 | Subject to change without notice.

800.348.5580

630.208.2200

#### APPLICATION NOTE: Understanding Thermal Analysis of RF Devices

The thermal performance of a PC board material is entirely dependent on the way the copper is laid out. To move heat downward to where a heatsink is attached you will need to use thermal vias at a minimum. These are drilled holes plated with copper to provide thermally conductive pathways from one copper layer to the next. The thicker the copper, the better, and it does provide a great conductor for heat to dissipate, but the more copper used, the higher the cost. So, both system designers and PC board manufacturers must consider tradeoffs regarding the amount of copper used.

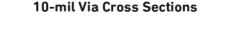

For example, for multi-layer PC boards built on FR4, common sizes for drilled and copper-plated thermal vias are 10-mil and 12-mil diameter. For Rogers' materials, thin two-layer boards and 8-mil thermal vias are common. See above in Table 1.

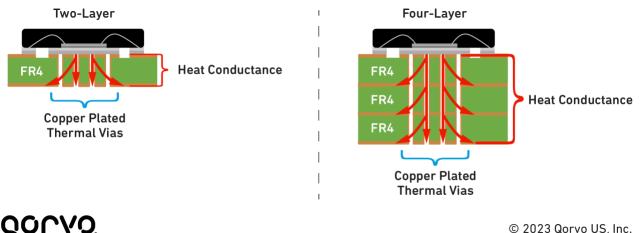

Another consideration in PC board layout and materials is the layer count. Many applications today have introduced several layers of a PC board to route all the complex connections between circuit components and features. But those additional layers also provide a benefit when addressing heat. In lower-power applications adding layers to the PC board has a big impact on heat conduction away from components. The difference between a two-layer and a four-layer board can be as much as 20°C depending on how well the copper planes are laid out for heat spreading. The four layers help to move the heat as shown in Figure 10. The various dielectric and copper layers impact the PC boards' thermal conductance below the device. The copper layers will dominate the heat flow because the copper k-value is high. In the FR4 layers, the k-value is low, so it is best to use the vias with copper plating to provide the thermal path from one copper layer to the next. But ultimately from a thermal low-power perspective, the more PC board layers, the better.

Although adding layers of PC board is a benefit in a low-power situation, doing so in high-power applications has the opposite effect. Adding PC board layers in applications such as GaN high-power devices, especially above 10 to 15 Watts of power, increases resistance and interferes with the heat path. Instead, in applications where a heat path must be optimum, like in high-power dissipation scenarios -a thin PC board is recommended rather than a multi-layered PC board. We will review this further in the GaN applications section in this application note.

© 2023 Qorvo US, Inc.

Figure 10. Heat Conductance – two-layer versus 4-layer PCB.

August 2023 | Subject to change without notice.

Richardson Electronics

# QONOD

### **Thermal Vias in an Application**

For many semiconductor components, the exposed pad underneath the part is electrically connected to ground. This area is usually the most convenient place for inserting copper for heat transfer. This is where thermal vias are used.

Using these vias, the thermal resistance can be significantly lowered. The placement, size and number of vias used in creating a thermal via array within the die pad area are critical. Maintaining a copper ground-plane on the top or bottom copper layer with as few breaks as possible to create a heat spreader on the PC board is recommended. In multi-layer PCBs, successive vias between copper layers should be aligned with the vias running between the top two metal layers (don't stagger them – make sure the heat can travel directly downward wherever possible).

Ultimately to determine these variables, it is recommended to take thermal measurements and perform thermal modeling to accurately create the most optimum number, size or type of via needed in your desired application. Ideally, it would be best to have solid vias and as many as possible underneath the die pad, so the maximum amount of heat is transferred, but this is not cost-effective nor practical. So, the best practice is to use the guidance of the semiconductor vendor as they will be able to provide optimized PC board files showing the location, type and number of thermal vias that should be used.

In regard to via holes used to remove heat from the device, thicker copper plating means a higher effective k-value of the total via cross-section and better heat transfer. In **Figure 11**,  $k_{EFF}$  or k effective, k refers to the effective thermal conductivity. The effective overall  $k_{EFF}$  value for the via cross sections increases as more copper plating is used. For example,  $k_{EFF} = 282$  W/(mK) for, a .010" diameter via with two-ounce plated copper, but  $k_{EFF} = 91$  when half-ounce copper is used. PCB designers must make tradeoffs on the cost vs. the effectiveness of thermal vias, but more copper is always better.

Figure 11. Comparison of thermal conductivity (k) of Cu via holes.

Some designs such as high-power GaN require via holes to be solid copper rather than relying on solder filled. Based on our internal analysis we recommend customers use a copper-plated solid via but do not advise fully plated vias using solder, as it may lead to voiding at the package interface. Also, for GaN operating above 10 or 15 W of power we recommend a thermal analysis, which may show the need for the device to be mounted using a copper coin under the package or die. We delve deeper into this topic in the GaN section of this document.

Another consideration in thermal vias is breaks in the thermal path. Effective heat spreading across the PC board improves the overall heat transfer. Adding traces too close to or perpendicular to the heat flow path near the source will hamper heat spreading and create hot spots. If traces are unavoidable due to design, attempt to make them run parallel to the predominant heat transfer path rather than across it.

August 2023 | Subject to change without notice.

**Richardson Electronics**

ER & MICROWA

### **Thermal Interfaces**

Generally, when putting two surfaces together, like a ground slug of the underside of a QFN package and a PC board, there is an expectation that the two solid metal bodies have smooth surfaces that bond well. However, this is far from reality as these surfaces have air gaps at the microscopic level. When two solids meet, the actual surface area touching is relatively small, which is the opposite of what one may think.

Heat will flow across and between the air gaps, but it will not flow as easily without the help of a thermal conductor such as thermal grease or other interface material. There are two main types of thermal interfaces:(1) bonded thermal interface (e.g., solder joints, sintering metal pastes, and epoxies), (2), compressible thermal interface materials.

Solders and sintering metal pastes form metallurgical bonds and are thermally the highest-performing interfaces. Epoxies are usually doped with thermally conductive particles like silver to improve their thermal performance. Solder joints have the advantage of being reworkable, while the sintering metal pastes and epoxies are not re-workable once hardened.

For packages such as QFNs that are normally soldered down, it is a good practice to minimize solder joint voids between the exposed pads and interconnections. There is a tradeoff between solder paste coverage and having the package "float" or "skate" on the PC board connection. Typically, the preferred solder paste coverage is 50% to 80%. On the ground slug, 80% coverage is preferred.

Compressive thermal interface materials (TIMs) are generally lower-performing and place structural requirements on components, PCBs, and heat sinks. Examples include thermal greases and graphite shims which must be held under compression to work effectively, meaning the two parts in contact must be stiff enough to handle the stress. Using thermal grease (e.g., Dow Corning 340) does not require mounting holes on the cold plate, because there is enough adhesion due to the grease layer surface tension. They are popular because they are easily re-workable. While these TIMs may have performance comparable to an epoxy-bonded interface, they can't approach the thermal performance of a good solder joint. Additionally, graphene film is also good for a TIM as long as there is sufficient pressure to obtain an optimal heat transfer.

### **Thermal Measurement Methods for an Application**

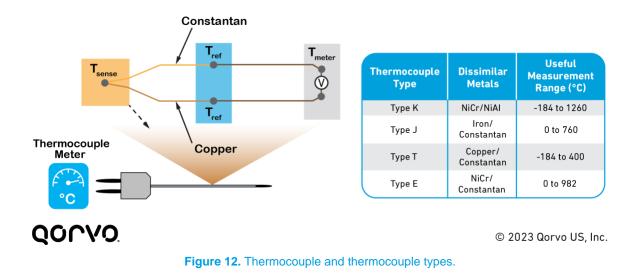

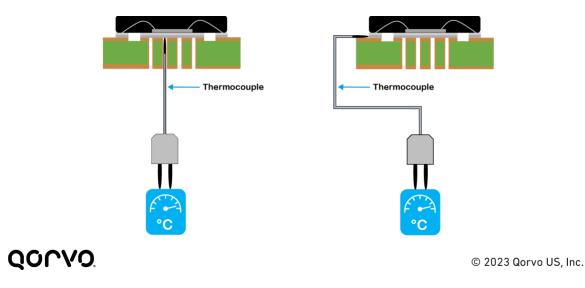

There are several methods used to determine the temperature in an application. One such method is modeling; another is IR imaging as we described above. Models are often used to determine temperatures in applications, but at times empirical measurements-are required. Thermocouples or thermistors may be used. A thermocouple measures using a voltage, and a thermistor uses electrical resistance, changing its physical resistance when exposed to changes in temperature.

Thermocouple measurements are one of the most commonly used sensing methods in engineering labs. (See **Figure 12**) Thermocouple measurements are simple and consist of two wires of dissimilar metals joined together at one end. The other end, where the wires are not joined, is connected to a multimeter or thermocouple meter. The junction of the two dissimilar metals (e.g., copper and constantan), produces a thermoelectric effect which gives a constant potential difference of only a few millivolts between them. Since the thermocouple is a differential device rather than measuring an absolute temperature, the reference junction temperature must be known.

rellpower.com rellpower@rell.com

As shown above, in Figure 12, thermocouples can be made from a variety of different materials, enabling measurement of extreme temperatures from -200°C to over 2000°C – the examples shown are the most commonly used in electronics. When using the thermocouple to measure temperature in a PCB with a device mounted on it, one should make certain to get as close as possible to the ground slug located under the packaged part, so the measured value is accurate to determine the true Rth.

### **High-Power GaN Application Considerations**

#### **Thermal Measurement**

For performing thermal analysis of GaN devices and MMICs, it is recommended to use an integrated approach that leverages device modeling, empirical measurements (including micro-Raman thermography), and finite element analysis (FEA) simulations. (See **Figure 13** and link below). This methodology has proven to be the most effective and accurate. Using this approach, once the baseline thermal model development is completed, FEA is employed to accurately predict channel temperature and thermal resistances at the device-level. Click on this link to view a short video on GaN thermal measurement.

## QORVO

© 2023 Qorvo US, Inc.

800.348.5580

630.208.2200

Figure 13. Tutorial video: Understanding GaN Thermal Analysis.

August 2023 | Subject to change without notice.

Richardson

Electronics

13 of 19

If micro-Raman thermography and FEA modeling are not an option and only an infrared (IR) camera is available, the accuracy limitations of IR imaging must be clearly understood. IR cameras have a spatial resolution that is an order of magnitude larger than the gate length of a FET channel and yield area-averaged surface temperatures which are much lower than the true maximum channel temperature. It is recommended to work closely with the GaN device applications teams to ensure the GaN device is operating cool enough in your application. The applications team can also provide a product bulk thermal model to drop into your system-level thermal model to estimate the device operating environment more accurately in your system-level model and determine the resulting junction or channel temperature.

#### **Improving Thermal Conductivity in Applications**

#### **Die Only Applications**

For GaN die components, the die should be mounted directly onto a thermally conductive heat sink material or onto an intermediate carrier plate (e.g., die-on-tab). It should be mounted using a gold-tin eutectic solder (preferably) or high thermal conductivity epoxy to mount the die. The heat sink can be integrated with the next-level assembly, or the die-on-tab can be mounted directly on a heat sink in the next-level assembly using solder or conductive epoxy. Refer to the application note referenced in the document; *GaAs and GaN Die Assembly and Handling Procedure.*

Gold-tin solder and many thermally conductive epoxies have a low thermal resistance value and the ability to accommodate coefficient of thermal expansion (CTE) mismatch stress (often seen when mounting GaN die to high thermal conductivity materials). It is important to ensure the gold-tin solder joint is void-free, especially under the active area of the die. If using a conductive epoxy, the attachment must be uniform and void-free, and have a thin bond line (to maximize thermal conductance).

Mounting a GaN die power device directly onto a PCB is not recommended unless it is mounted to a high-thermal-conductivity coin (e.g., a copper coin) to ensure adequate heat transfer.

#### **QFN and Surface Mount Packaged Applications**

GaN QFN and surface mount packaged components are mounted directly to a PC board. These GaN amplifiers are generally used in intermediate power dissipation applications either in CW mode or in pulsed applications. In these applications copper thermal vias are needed to provide a thermally conductive path to the system heat sink. The via size, placement, type, and amount of copper plating should be selected to optimize the overall thermal conductance of the PCB design. For GaN QFN packages, it is preferred to keep the PCB thickness very thin (e.g., .008 inches) to keep the thermal resistance low. Using a thin PCB with a dense via array is important, especially for high frequency GaN MMICs.

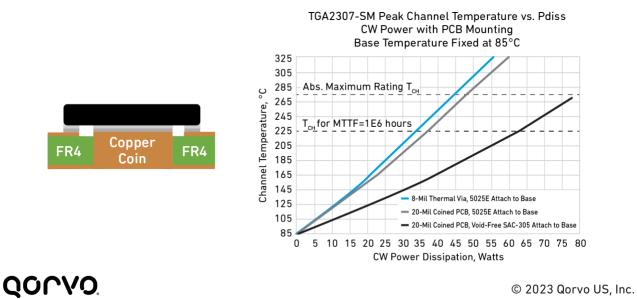

Conductive paths are usually the most efficient way to remove heat from a device. For QFN and surface mount packaged amplifiers having an area-averaged CW heat flux > 1 W/mm<sup>2</sup> out of the bottom of the package, the use of a coined PCB is highly recommended to provide a good thermal path to the system heat sink (see **Figure 14** for an example of the impact). Anything above 2 W/mm<sup>2</sup> should definitely have a copper coin under the package. A good reference document on this topic is the Application Note: *CW Operation of QFN-Packaged Pulsed GaN Power Amplifiers*. As you can see from the below figure and the application note – above 10 to 15 Watts, it is best to use a PCB with a copper coin to ensure the reliability and performance criteria of your application can be met.

August 2023 | Subject to change without notice.

Richardson Electronics

**6**

Figure 14. Example of copper coin structure under GaN device and via versus coined comparison.

#### **Copper Plated (CP) and Flange Packaged Applications**

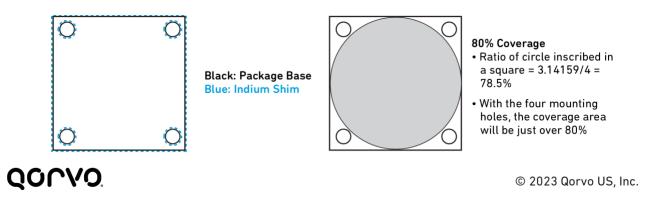

Providing a good thermal interface between a high-power GaN packaged transistor or packaged MMIC and its heat sink is paramount. Poor package-attach is a major cause of thermal failure. In high-power situations, Qorvo recommends employing a 2 to 4 mils thick (~50-100  $\mu$ m) thermal interface material (TIM) made from a thermally conductive material (e.g., indium sheet or graphite film), or a 1 to 2 mils (~25-50  $\mu$ m) thick layer of thermal grease or thermal compound, covering the entire package base area for mounting flange-based packages.

One thing to note with TIMs is that sufficient pressure is required for obtaining good heat transfer. When using a thermal grease or a thermal compound, minimum of 80% coverage is required. Refer to **Figure 15** for recommended use of an indium shim or thermal compound.

Figure 15. Example of indium shim and thermal compound under packaged GaN devices.

### **System Level Thermal Analysis**

A successful system-level design relies heavily on having a good heat path from the semiconductor to the external environment. Careful consideration of the heat flow path is needed at all levels – device, package, PCB, and final heat sink. High-power GaN devices will require fan-cooled finned heat sinks or liquid cooling systems for adequate cooling.

Semiconductor reliability is partly defined by estimating a device's maximum junction or channel temperature to determine a projected lifetime. These values are gathered by measuring and modeling thermal resistance, power dissipation and heat transfer. In an application, the maximum junction or channel temperature is a key metric and depending on a single method is not good practice; thermocouple/thermistor measurements, modeling, IR imagery, etc., should all be employed. In a package such as the one shown in **Figure 16**, one should use a model to determine the maximum case temperature under the device for the purpose of estimating the junction temperature based off package thermal resistance. Note – for GaN components refer to the application note *GaN Device Channel Temperature, Thermal Resistance and Reliability Estimates.*

Figure 16. Thermal case measurement of a packaged device.

Another nice-to-have in system level thermal analysis is having a bulk thermal model of the semiconductor component. Having this model from a semiconductor supplier will help customers mimic the output heat flux of the component helping customers estimates of maximum backside temperature of the product and what it will experience when operated in the customer system design. In addition, the bulk thermal model provides greater insight into how neighboring devices are impacted by the waste heat from Qorvo's product.

The junction or channel-to-base temperature, as shown in **Figure 17**, uses a thermocouple to provide the temperature of the package base. While this is possible, care should be taken to ensure that the thermocouple is reading the proper region. As shown in Figure 16, the measurement should be taken at or as close to the underside of the package ground pad as possible. If the measurement is done at the pad location, it is recommended that more analysis be done, such as modeling the system using a product bulk thermal model.

August 2023 | Subject to change without notice.

# QOUND

APPLICATION NOTE: Understanding Thermal Analysis of RF Devices

Once this case temperature is known, the next step is to calculate the power dissipation. Qorvo has an online calculator to make this easy. (Qorvo online  $PAE/P_{diss}/T_j$  calculator – see Figure 18). The online calculator can also be used to calculate the power dissipation and the maximum junction temperature of a component. Link to calculator.

| TEP 1: CALCULATE POWER (                                                                                                                                                                                                                          | DISSIPATION IN DEVICE (PDISS)                                                                                                                   | • D(                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| ready know your Pdiss? Enter it below j                                                                                                                                                                                                           |                                                                                                                                                 | • Ga                                                                                                   |

| -Inputs-                                                                                                                                                                                                                                          | Outputs                                                                                                                                         | • Pi                                                                                                   |

| Supply:<br>28 Volts                                                                                                                                                                                                                               | DC Power:<br>154.00 Watts                                                                                                                       | • P(                                                                                                   |

| Current:<br>5500 mA                                                                                                                                                                                                                               | Gain:<br>20 dB                                                                                                                                  | - Di<br>(P                                                                                             |

| Pin:<br>30 dBm ∨                                                                                                                                                                                                                                  | Drain/Collector Efficiency:<br>64.935 %                                                                                                         |                                                                                                        |

| Pout:<br>50 dBm V                                                                                                                                                                                                                                 | Power Added Efficiency:<br>64.286 %                                                                                                             | • P/<br>(P                                                                                             |

|                                                                                                                                                                                                                                                   | Power Dissipated In Device (Pdiss):<br>55 Wats                                                                                                  | • Pe                                                                                                   |

|                                                                                                                                                                                                                                                   |                                                                                                                                                 |                                                                                                        |

| Power Dissipated In Device (Pdiss):                                                                                                                                                                                                               |                                                                                                                                                 | • M<br>Ca<br>Ca                                                                                        |

| Power Dissipated In Device (Pdiss):                                                                                                                                                                                                               | 55 Watts                                                                                                                                        | са<br>Са                                                                                               |

| Power Dissipated In Device (Pdiss):                                                                                                                                                                                                               | 55 Watts ICTION TEMPERATURE Outputs                                                                                                             | Ca                                                                                                     |

| Power Dissipated In Device (Pdiss):<br>TEP 2: CALCULATE MAX JUN<br>Inputs<br>Maximum Case (Tbase) Temperatu<br>[85                                                                                                                                | 55 Watts ICTION TEMPERATURE re: Outputs Max Junction Temperature:                                                                               | са<br>Са                                                                                               |

| Power Dissipated In Device (Pdiss):<br>TEP 2: CALCULATE MAX JUN<br>Inputs<br>Maximum Case (Tbase) Temperatu<br>[85                                                                                                                                | 55     Watts       ICTION TEMPERATURE     Outputs       re:     Max Junction Temperature:<br>173                                                | دی<br>2<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| Power Dissipated In Device (Pdiss):<br>TEP 2: CALCULATE MAX JUN<br>-Inputs<br>Maximum Case (Tbase) Temperatu<br>85 °C<br>Rth Junction To Case:<br>1.6 °C/                                                                                         | 55     Watts       ICTION TEMPERATURE     Outputs       re:     Max Junction Temperature:       173     °C       watt     ation and measurement | Ca<br>Ca<br>Oth<br>• Te<br>Ri                                                                          |

| Power Dissipated In Device (Pdiss):<br>TEP 2: CALCULATE MAX JUN<br>Inputs<br>Maximum Case (Tbase) Temperatu<br>85 °C<br>Rth Junction To Case:<br>1.6 °C<br>Note:<br>Measured values vary based on applic<br>method. The most accurate data is loc | 55     Watts       ICTION TEMPERATURE     Outputs       re:     Max Junction Temperature:       173     °C       watt     ation and measurement | دی<br>2<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

#### Formulas Used

- DC Watts = Supply V × Current/1000

- Gain (dB) = Pout dBm Pin dBm

- Pin Watts = (10^(Pin dBm/10))/1000

- Pout Watts = (10<sup>(Pout dBm/10)</sup>)/1000

- Drain/Collector Efficiency % = (Pout Watts/DC Watts) × 100

- PAE % (Low Gain < 25dBm) = (Pout Watts - Pin Watts) x 100/(DC Watts)

- Pdiss Watts =

DC Watts + Pin Watts Pout Watts

- Max. Junction Temperature at Max. Case Temp = Temp Change °C + Max. Case Temp °C

#### **Other Formulas**

- Temperature Change °C = Rth Junction to Case × Pdiss Watts

- Tbase = Interface Between Part and PC Board/Heat Sink

800.348.5580

630.208.2200

© 2023 Qorvo US, Inc.

Richardson

**Electronics**

POWER & MICROWAVE TECHNOLOGIES

August 2023 | Subject to change without notice.

Technology

Partner

17 of 19

As noted earlier, there is a Qorvo video showing how to use this calculator with GaN components. The link to that video is here, Understanding GaN Thermal Analysis. For general applications, let's review a case study to assist in a better understanding of how this calculator can be used.

Using the PAE /  $P_{diss}$  /  $T_J$  calculator:

- 1. In STEP 1 of the calculator, enter the supply voltage, operating current, input power, and output power of the device.

- 2. The outputs to these values are displayed in the calculator, including Power Dissipated in Device (Pdiss).

- 3. Enter the maximum case (TBase) temperature and Rth (J-C) from the data sheet under "STEP 2" to see the Max. Junction Temperature. If you already know dissipated power, you may enter it under "Already know your P<sub>diss</sub>?" and enter the two "STEP 2" inputs to see the Max. Junction Temperature.

### **In-Closing**

Understanding and determining the thermal performance of both semiconductor devices and system designs are critical to ensuring your product functions optimally, reliably and without problems. Although this application note does not replace the method of finite element analysis and the software tools used in such measurements and analysis, it does provide guidance in thermal analysis design. Using the outlined methods and tools will aid system engineers with design considerations and thermal measurements.

### **Definitions**

- Junction or Channel Temperature The highest operating temperature of the actual semiconductor in an electronic device.

- Absolute Maximum Junction or Channel Temperature The temperature beyond which damage occurs to the semiconductor device after a specific amount of time. The device may not function or meet the expected performance at this temperature.

- Absolute Maximum Operating Temperatures The maximum environment temperature where the device is recommended to operate. Operating above this temperature can damage or reduce the lifetime of the device. This is sometimes referred to as the case temperature.

- Thermal Conductivity The ability of a given material to conduct/transfer heat.

- Thermal Resistivity The ability of a given material to resist the conduction/transfer of heat.

- Thermal Resistance Is like resistivity but takes the shape and size of the material into account.

- **Thermal Impedance** Is like resistance but does not factor in the footprint size of the material and often includes interfacial resistances to provide an effective value for a layer within a stack.

# QOLVO

### **Additional Information**

For information on ESD, soldering profiles, packaging standards, handling and assembly, please contact Qorvo for general guidelines.

### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations:

Web: www.qorvo.com

Tel: 1-844-890-8163

Email: customer.support@qorvo.com

© 2023 Qorvo US, Inc. All rights reserved. This document is subject to copyright laws in various jurisdictions worldwide and may not be reproduced or distributed, in whole or in part, without the express written consent of Qorvo US, Inc. | QORVO® is a registered trademark of Qorvo US, Inc.

August 2023 | Subject to change without notice.

Richardson Electronics POWER & MICROWAVE TECHNOLOGIES